# ETS 2019

### 24rd IEEE European Test Symposium

May 27 - May 31, 2019 Baden-Baden, Germany

## Program

## GEMEINSAM IN DIE ZUKUNFT – GESTALTEN WIR DIE WELT VON MORGEN

#### Wir sind Advantest

Advantest ist ein weltweit führender Entwickler und Hersteller von automatischen Testsystemen und innovativen Applikationslösungen für die Halbleiter- und Automotive-Industrie. Mit rund 5000 Mitarbeitern an vielen Standorten rund um den Globus entwickeln wir innovative Testlösungen auf höchstem technologischen Niveau.

#### **Unsere Produkte**

Ob Unterhaltungselektronik, mobile Kommunikation oder ganze Computernetzwerke - in all diesen Produkten stecken winzige Chips, die unzählige Aufgaben erledigen - und diese in einer atemberaubenden Geschwindigkeit. Jeder Chip eines High-Tech Produktes durchläuft in jeder Phase des Entwicklungs- und Produktionsprozesses zahlreiche, komplexe Tests. Die hochkomplexen Testsysteme von Advantest prüfen und stellen dabei die einwandfreie Funktion sicher.

#### Wir gestalten die Welt von morgen

Einer der wichtigsten Forschungs- und Entwicklungsstandorte von Advantest ist in Böblingen. Hier werden neueste Technologien im Bereich Halbleitertest für namhafte Kunden weltweit entwickelt. Hochqualifizierte und engagierte Mitarbeiter sind hierbei der Schlüssel zu unserem Erfolg.

#### Karriere und Jobs

Ob Experte oder Berufseinsteiger, informieren Sie sich auf unserer Career Seite über die interessanten Stellenangebote. Darüber hinaus bieten wir mit unseren Angeboten an Dualen Studiengängen und Ausbildungsprogrammen einen erfolgreichen Start in Ihre Karriere.

www.advantest.com

## Program Guide

| Foreword                | 2  |

|-------------------------|----|

| Committees              | 6  |

| General Information     | 10 |

| Keynotes                | 12 |

| Panels                  | 16 |

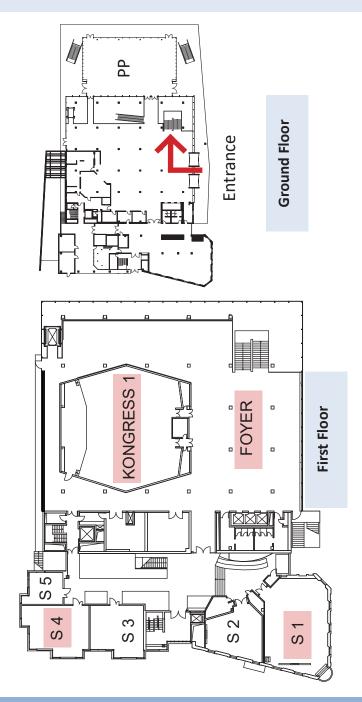

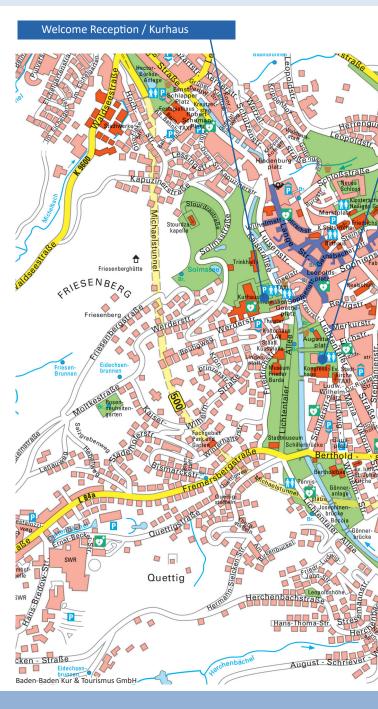

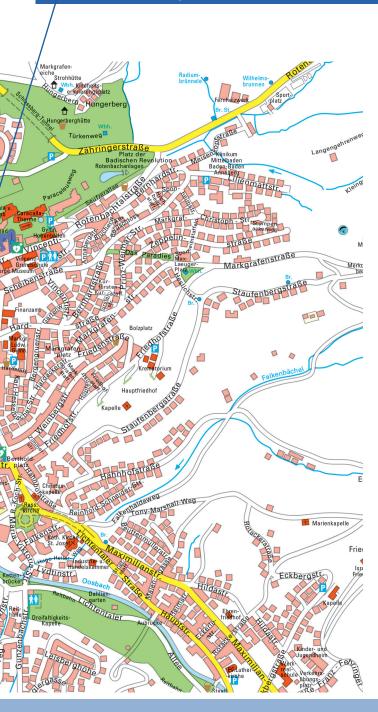

| Map of the Venue        | 18 |

| New Program Initiatives | 20 |

| Vendor Sessions         | 20 |

| Monday, May 28, 2018    | 21 |

| Tuesday, May 29, 2018   | 22 |

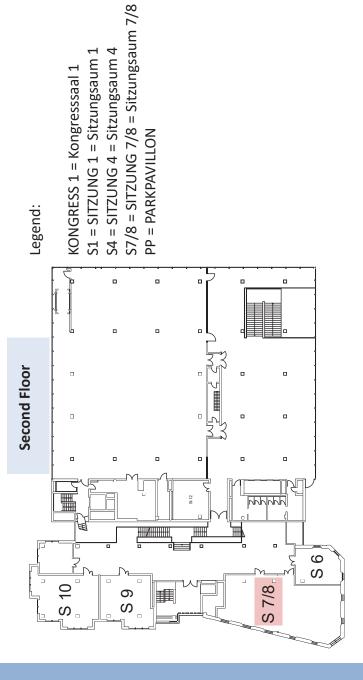

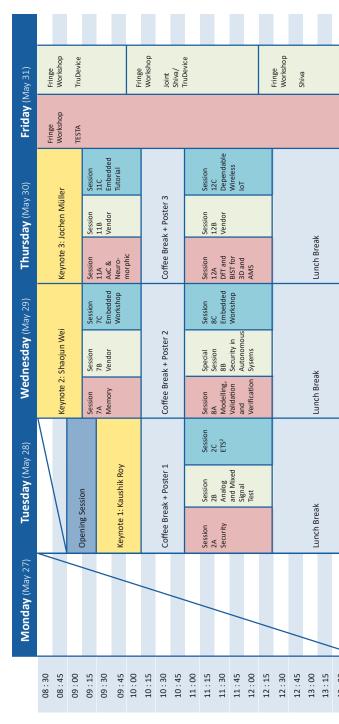

| Program at a Glance     | 24 |

| Wednesday, May 30, 2018 | 29 |

| Thursday, May 31, 2018  | 34 |

| Fringe Workshops        | 38 |

| Fringe Meetings         | 41 |

| Welcome Reception       | 42 |

| Social Activities       | 44 |

| Local Map               | 46 |

| Notes                   | 48 |

## Welcome

n behalf of the Program, Organizing, and Steering Committees. we would like to extend a warm welcome to everyone attending the European Test Symposium 2019, FTS has been established as one of the main international forums and the largest one in Europe that brings together the test community to present and discuss scientific results, emerging ideas, applications, hot topics. and new trends in the area of electronic-based circuit and svstem testing and reliability as well as in the fields of verification and security aspects in test. Topics of interest include but are not limited to, design-for-test, dependability, security, failure analysis and diagnosis, on-line test, automated test hardware, validation and verification, fault simulation, fault tolerance, automatic test generation, test of emerging architectures and technologies, etc.

This year ETS takes place in Baden-Baden, Germany, and is organized by the Karlsruhe Institute of Technology (KIT), which cosponsors the event jointly with the **IEEE** Council on Electronic Design Automation (CEDA). Baden-Baden was established over 2,000 years ago as a place for people to relax and reconnect with themselves. Water, light, earth, and air are the city's precious resources. As the pearl of the Black Forest. extraordinary hot springs, spas and nature, hotels of unparalleled quality - and the lure of the casino, are among its attractions. Over the centuries. Baden-Baden has evolved into an enchanting destination, offering a spectacularly diverse range of opportunities for both relaxation and excitement. Its Museum Mile exhibits up-andcoming artists alongside the works of both old and contemporary masters.

ETS is the cornerstone event of the European Test Week, which includes in addition the Test Spring School (TSS) and Fringe Workshops. The main topic for this year's TSS, which precedes the symposium, is Cutting Edge Approaches for Test. Three Fringe Workshops will take place immediately following ETS'19, namely the 4th International Test Standards Application (TESTA) Workshop, which focuses on test standards, the 8th Workshop on Trustworthy Manufacturing and Utilization of Secure Devices (TRUDEVICE), as well as the Secure Hardware, Integrity and preVention of Attacks Workshop (SHIVA).

ETS'19 received a significant number of scientific paper submissions from 28 countries all over the world. Each paper was evaluated by on average 5 expert reviews. Based on the written reviews and follow-up online discussions among the reviewers, the Organizing Committee and the Topic Chairs convened in Karlsruhe, Germany, on February 8, 2019, and recommended to accept 25 papers for oral presentation, distributed over 9 regular sessions, and 13 papers for poster presentation, distributed over 3 poster sessions. An Award Committee has been formed and will select the best paper based on the reviewers' comments and the ratings provided by the attendees. The authors of the

best paper will receive the Best Paper Award during the opening ceremony of ETS'20. Apart from scientific paper presentations and posters, the ETS'19 program consists of 3 plenary keynote addresses, 2 one-hour embedded tutorials and 2 TSS@ ETS Monday tutorials, 2 panel sessions, 3 special sessions, the PhD contest, and several vendor sessions. In addition, ETS features again a special session on Emerging Test Strategies (ETS<sup>2</sup>), where new issues are presented by the industry and are discussed in an informal atmosphere. Furthermore, the new Embedded Workshop track is dedicated to work in progress and case studies, while the newly established PhD Forum provides an excellent opportunity for PhD students to present their ongoing work and get feedback from experts in the field. Finally, the ETS'19 program is enriched with an exciting social program providing superb opportunities for informal discussions among participants in a relaxed setting. The social activities start with a welcome reception and

continue with the main social event on Wednesday. This includes to the ETS'19 corporate spona guided city tour with historical, cultural and music flavors. The social event ends with a relaxing gala dinner at the "Geroldsauer Mühle" in the outskirt of Baden-Baden and the gate to the Black Forest.

ETS'19 is the result of the hard work of many dedicated volunteers involved in the technical and organizational activities leading to the European Test Week. We wholeheartedly thank all of them for their significant effort to put together this edition of ETS. We also thank all authors who submitted their work to ETS'19, the presenters for their contributions. and all attendees for their active participation. We also thank the IEEE Council on Electronic Design Automation and the IEEE Computer Society Test Technology Techni- Jaan Raik cal Council for the continued technical sponsorship and support. We particularly thank German **Research Foundation - Deutsche** Forschungsgemeinschaft (DFG) for their financial and technical support as well as Karlsruhe Institute of Technology (KIT) for their organizational support. Last but

not least, we extend our thanks sors: Advantest, ARM, Cadence, Infineon, Intel, Mentor Graphics, Ridgetop Europe and Synopsys, for their financial sponsorship and continued support of ETS.

We are excited about the strong lineup of ETS'19 and overall of the European Test Week. We are confident that you will find it a beneficial and exciting experience with lots of networking opportunities for researchers, developers and vendors. We wish you all a fun-filled and productive week in Baden-Baden!

Mehdi Tahoori General Chair

Artur Jutman General Vice-Chairs

Svbille Hellebrand **Program Chair**

**Görschwin Fey Program Vice-Chair**

Trinkhalle

## Join us!

## Test & Repair for SoC Memories and Hierarchical Test for AMS & PHY IP

Tutorial | Yervant Zorian, Synopsys Fellow | Wednesday, May 29; 09:15 – 09:45 - Session 7B

## Maintaining Automotive Quality for Next-Generation Microcontrollers

Joint Presentation | Vladimir Litovtchenko, Synopsys; Ralf Arnold, Infineon Technologies; Johanna Sepulveda TU - Munich | Tuesday, May 28; 14:00 – 15:30 - Session 3A

www.synopsys.com/designware-ip

## **Organizing Committee**

General Chair Mehdi Tahoori (DE)

Program Chair Sybille Hellebrand (DE)

General Vice-Chairs Artur Jutman (EE) Jaan Raik (EE)

Program Vice-Chair Görschwin Fey (DE)

Local and Financial Chair Iris Schroeder-Piepka (DE)

Topic Chairs Paolo Bernardi (IT) Alberto Bosio (FR) Artur Jutman (EE) Martin Keim (US) Régis Leveugle (FR) Maria Michael (CY) Ilia Polian (DE) Christoph Scholl (DE) Haralampos Stratigopoulos (FR) Ioana Vatajelu (FR)

ETS<sup>2</sup> Special Track Chairs Rene Segers (NL) Zebo Peng (SE)

Embedded Workshop Chairs Pete Harrod (UK) Gildas Leger (ES) Jochen Rivoir (DE)

Panel Chairs Jeff Rearick (US) Matteo Sonza Reorda (IT) **Embedded Tutorial Chairs** Lorena Anghel (FR) Teresa McLaurin (US)

Special Session Chairs Bernd Becker (DE) Krishnendu Chakrabarty (US)

PhD Forum Chairs Liviu Miclea (RO) Ernesto Sanchez (IT)

PhD Contest Chairs Said Hamdioui (NL) Alberto Bosio (FR)

Industrial Relation Chairs Hans Manhaeve (BE) Jürgen Schlöffel (DE)

Publication and Review Chair Giorgio Di Natale (FR)

Publicity Chairs Stefano Di Carlo (IT) Michiko Inoue (JP) Web Chair Alessandro Savino (IT)

Award Chairs Peter Maxwell (US) Jerzy Tyszer (PL)

ETS Fringe Workshop Chairs Maxim Jenihhin (EE) Erik Larsson (SE)

#### **Regional Liaisons**

Asia: James Chien-Mo Li (TW) Huawei Li (CN) South Pacific: Adam Osseiran (AU) India: Virendra Singh (IN) South America: Letitia Pöhls (BR) North America: Adit Singh (US) Nicola Nicolici (CA)

#### **TSS Chairs**

Lorena Anghel (FR) Sybille Hellebrand (DE) TSS Local Arrangement Chair Dennis Gnad (DE)

#### **Steering Committee**

Matteo Sonza Reorda (IT) - Chair Lorena Anghel (FR) Bernd Becker (DE) Rolf Drechsler (DE) Stephan Eggersglüß (DE) Joan Figueras (ES) Patrick Girard (FR) Said Hamdioui (NL) Pete Harrod (GB) Sybille Hellebrand (DE) Artur Jutman (EE) Hans Manhaeve (BE) Erik Jan Marinissen (BE) Maria Michael (CY) Liviu Miclea (RO) Zebo Peng (SE) Jaan Raik (EE) Michel Renovell (FR) Jochen Rivoir (DE) Mehdi Tahoori (DE) Hans-Joachim Wunderlich (DE) Yervant Zorian (US)

Local Organizing Committee

Iris Schroeder-Piepka (DE) iris.schroeder-piepka@kit.edu

Dennis Weller (DE) dennis.weller@kit.edu

# arm

# Automotive Solutions

Join our talk to discover Arm's latest IP solutions for functional safety applications, including the recently launched Arm Cortex-A76AE.

For more information, please visit:

## arm.com/solutions/automotive

#### Program Committee

Juergen Alt (DE) Paolo Amato (IT) Davide Appello (IT) Daniel Arumi (ES) Luz Balado (ES) Manuel Barragan (FR) Cristiana Bolchini (IT) Gabriele Boschi (IT) Andreas Burg (CH) Ramon Canal (ES) John Carulli (US) Wim Dobbelaere (BE) Piet Engelke (DE) Marie-Lise Flottes (FR) Valentin Gherman (FR) Emil Gizdarski (US) Dimitris Gizopoulos (GR) Daniel Grosse (DE) Gurgen Harutyunyan (AR) Stefan Holst (JP) Jiun-Lang Huang (TW) Ke Huang (US) Naghmeh Karimi (US) Ramesh Karri (US) Hans Kerkhoff (NL) Rene Krenz-Baath (DE) Bram Kruseman (NL) Wolfgang Kunz (DE) Yiorgos Makris (US) Nele Mentens (BE) Salvador Mir (FR)

Farshad Moradi (DK) Grzegorz Mrugalski (PL) Stelios Neophytou (CY) Martin Omaña (IT) Alex Orailoglu (US) Panagiota Papavramidou (FR) Rubin Parekhji (IN) Antonis Paschalis (GR) Jean Michel Portal (FR) Janusz Rajski (US) Paolo Rech (BR) Sudhakar Reddy (US) Rosa Rodriguez (ES) Daniele Rossi (UK) Adoración Rueda (ES) Matthias Sauer (DE) Melanie Schillinsky (DE) Mario Schoelzel (DE) Johanna Sepulveda (DE) Muhammad Shafique (AT) Stephen Sunter (CA) Mottagiallah Taouil (NL) Daniel Tille (DE) Nur Touba (US) Yiorgos Tsiatouhas (GR) Federico Venini (IT) Ingrid Verbauwede (BE) Arnaud Virazel (FR) Hans-Martin von Staudt (DE) Xiaoqing Wen (JP) Vladimir Zivkovic (UK)

## **General Information**

#### Organizer

Karlsruhe Institute of Technology

#### Dates / Symposium Venue

| Date  | May 27 – 31, 2019           |

|-------|-----------------------------|

| Venue | Kongresshaus Baden-Baden    |

|       | Augustaplatz 10             |

|       | 76530 Baden-Baden           |

|       | Germany                     |

| Phone | +49 7221 304 -0             |

| Fax   | +49 7221 304 -304           |

| Email | info@kongresshaus.de        |

| Web   | https://www.kongresshaus.de |

#### **Registration / Information Hours**

| ETS/Workshops     | Registration desk (Foyer 1st Floor) |

|-------------------|-------------------------------------|

| Monday, May 27    | 13:00 - 19:00                       |

| Tuesday, May 28   | 08:00 - 20:00                       |

| Wednesday, May 29 | 08:00 - 16:00                       |

| Thursday, May 30  | 08:00 - 19:00                       |

| Friday, May 31    | 08:00 - 16:00                       |

#### Wifi Credentials (Kongresshaus)

| SSID :    | ETS2019      |

|-----------|--------------|

| Password: | badenETS2019 |

#### Proceedings

| Web:      | https://www.testgroup.polito.it/ets19/proceedings/ |

|-----------|----------------------------------------------------|

| Username: | ets2019attendee                                    |

| Password: | 3tspr0c33d1ngs2019                                 |

### Baden-Baden – The good-good life.

"The Belle Époque Meets The Age Of Instagram" is the headline the New York Times recently used to describe Baden-Baden – and it's certainly true that today the city's rich history blends seamlessly with a highly contemporary lifestyle. Baden-Baden was established over 2,000 years ago as a place for people to relax and reconnect with themselves. Water, light, earth and air are the city's precious resources. Extraordinary hot springs, spas and nature, hotels of unparalleled quality – and the lure of the casino. Over the centuries, Baden-Baden has evolved into an enchanting destination, offering a spectacularly diverse range of opportunities for both relaxation and excitement.

The Pulse Of The Contemporary Can Be Felt Everywhere In Baden-Baden: its Museum Mile exhibits up-andcoming artists alongside the works of both old and contemporary masters; the SWR3 New Pop Festival brings international stars to the city; the Festspielhaus hosts the world's leading orchestras; new and renowned hotels, restaurants and shops set new standards of excellence for the region – and far beyond. Visitors travel here from all around the world to spend lively nights in the bars and clubs.

Festspielhaus

### **Keynotes**

#### **Cognitive Computing: Design, Verification & Security Challenges**

Kaushik Roy Edward G. Tiedemann Jr. Distinguished Professor, Director of the center for brain-inspired computing (C-BRIC)

ABSTRACT:

Deep Learning has made tremendous progress in the recent past; even surpassing humans in some image recognition and gaming tasks. However, there are still several challenges to be addressed. There is orders of magnitude energy efficiency difference between natural intelligence and artificial intelligence. Their suitability in mission critical applications is still in question -- they are vulnerable to adversarial attacks, while the results obtained from such systems are not yet fully explainable and verifiable. In this talk I will present some of

the latest developments (and challenges) in brain-guided algorithms and hardware that can make deep learning systems more efficient and robust.

#### SHORT BIO:

Dr. Kaushik Roy is the Edward G. Tiedemann, Jr., Distinguished Professor of Electrical and Computer Engineering at Purdue University. He received his PhD from University of Illinois at Urbana-Champaign in 1990 and joined the Semiconductor Process and Design Center of Texas Instruments, Dallas, where he worked for three years on FPGA architecture development and low-power circuit design. His current research focuses on cognitive algorithms, circuits and architecture for energy-efficient cognitive computing, computing models, and neuromorphic devices. Kaushik has supervised 75 PhD dissertations and his students are well placed in universities and industry. He is the co-author of two books on Low Power CMOS VLSI Design (John Wiley & McGraw Hill). He has received several best paper awards. Dr. Roy is a fellow of IEEE and he is on the editorial boards of several IEEE journals.

#### Software Defined Chips: An Innovative Architecture Leading to

Shaojun Wei Director, Institute of Microelectronics, Tsinghua University

#### Intelligent Computing

ABSTRACT:

Intellectualization is a revolution that human society is experiencing, and it is also the core of the fourth industrial revolution. Obviously it ultimately depends on integrated circuit technology, because not only now, but also in the future for quite a long time, we cannot find other technologies that can replace integrated circuits. Therefore, we have no other options than using integrated circuit technology for implementing intelligence. It is also the

reason why people spend a lot of energy focusing on AI chips in the development of artificial intelligence. For a large number of artificial neural networks each of which corresponds to only one application, an integrated circuit that cannot be changed after manufacturing is obviously far from the requirements. Even devices such as FPGA, which are field programmable, can hardly meet the needs of AI development in terms of computing efficiency and energy efficiency. We urgently need to find an innovative chip architecture. This paper will focus on software definition chip (SDC), an innovative chip architecture that allows the chip function to dynamically change in real time with the change of software. SDC moves from traditional software adapting hardware to hardware adapting software. By gradually improving the intelligence of chip, SDC eventually moves to intelligent chip. Besides, the core of SDC is a dynamically reconfigurable PE array that not only has high computing efficiency and energy efficiency, but also improves the reliability of the chip through redundant design, and improve the ability to resist attacks by randomly configuring the space-time position of the sensitive circuits as well. In addition, based on dynamic reconfigurability, the potential security threats caused by test paths in DFT are also mitigated.

#### SHORT BIO:

Dr. Shaojun Wei is the professor of Tsinghua University and currently serves as the Dean of the Department of Micro- and Nano-Electronics and Director of the Institute of Microelectronics, Tsinghua University. He is also the adjunct professor of Peking University. Prof. WEI is the Vice President of the China Semiconductor Industry Association (CSIA), President of VLSI Design Chapter, CSIA. Prof. WEI is the President of Communication Specific IC Committee, China Institute of Communications (CIC) and the fellow of China Institute of Electronics (CIE). Prof. WEI is the chief scientist of State Key program of science and technology for integrated circuits.

#### Hold the reins in test engineering

Jochen Müller Director for all ASIC test developments at Bosch GmbH

#### ABSTRACT:

The lecture describes recent and upcoming trends in the automotive industry with its derived automotive ASIC requirements and drivers behind. In addition some pitfalls in requirements engineering with respect to customer needs, specifications and test realisation are presented. A supporting toolset is discussed to achieve a continuous flow and control of requirements

starting with the customer specification, followed by datasheet and ending in testing software. As an example, an eclipse based toolchain is presented with dedicated features for requirements control including automatic code generation of test programs out of this tool. This code supports ef-

ficient installation and execution on selected modern test systems.

#### SHORT BIO:

Dr. Jochen Müller joined Robert Bosch GmbH in 1996 and started in the technology area. He was head of the production wafer test facility of Bosch until he became director for all ASIC test developments within Robert Bosch's semiconductor development in Reutlingen/Germany in 2012. His main focus is currently set to Bosch's international test technology network. Prior to joining Robert Bosch GmbH, Jochen Müller got his PhD at University of Dortmund. He studied electrical engineering with key aspects on microelectronics.

Talk to our experts at ETS 2019 and find out more

# Shaping the future of automotive electronics

Market leader for electric drivetrains and CO<sub>2</sub> mitigation: We make cars cleaner.

Leading portfolio of sensors and security ICs for personal convenience and connectivity: We make cars smarter.

Market leader for ADAS: We make automated driving safer.

**TUESDAY, MAY 28, 2019** 18:00 - 19:30 SESSION 5: Wine and Cheese Panel

Organizer and Moderator: Jeff REARICK, AMD - US

#### The Test Industry Roadmap: Ask the Experts!

We'll continue our tradition of tapping the collective expertise of the ETS participants by hosting an interactive "Ask The Experts" session during the Wine and Cheese Panel. The twist is that anyone can ask a question and \_everyone\_ has the chance to be the expert who answers it (or contests the answer of another expert). The general theme is "The Test Industry Roadmap" but anything goes. Prizes will be awarded for best question, best answer, and best rebuttal.

#### WEDNESDAY, MAY 29, 2019 13:30 - 15:00 SESSION 9A: Panel

Organizer: Harry Chen, MediaTek - TW

#### System-level Test (SLT) - What does the Future Hold?

Panelists: John YI, AMD - US Marc HUTNER, Teradyne - CA Anil BHALLA, Advantest - US Carsten OHLHOFF, Continental Automotive - DE Adit SINGH, Auburn University - US Paolo BERNARDI, Politecnico di Torino - IT

Summary:

Testing of complex electronics-based systems is becoming more difficult and costly. To meet the challenge, can we count on enhanced structural test using advanced fault models such as

cell-aware? Or do we have to employ more system-level test (SLT)? Can a more methodical and standardized approach to SLT over current ad hoc practices be developed to achieve better cost efficiency? What about balancing the roles of traditional ATE and SLT testers for a more optimal test flow. Perhaps bring more SLT content upstream to wafer probe or include structural test content as part of in-system test? Is end-to-end test data analytics the solution to closing the diagnostic loop to identify the root causes of field failures? Should we be paying more attention to the role of embedded software when modern complex systems fail? What academic research topics will build the foundation for future system-oriented testing? These questions and possible approaches will be examined and debated by a panel of experts from industry and academia.

Casino

## Map of the Venue

## **New Program Initiatives**

This year ETS features two new program categories.

The Embedded Workshop targets work in progress as well as case studies. The sessions are characterized by an informal setup allowing for intensive interaction and lively discussions.

The PhD forum provides an excellent opportunity for PhD students to present their ongoing work and get feedback from experts in the field. It is organized as a special poster session on Tuesday afternoon. There will be an award for the best contribution to the Ph.D. Forum, which will be announced during the ETS'19 closing session.

## **Vendor Sessions**

More information on the Vendor Sessions can be found online at

https://www.testgroup.polito.it/ets19/vendor-session-presentations/

Kongresshaus

## Program

## MONDAY, MAY 27, 2019

| 14:00 - 16:00 TSS@ETS TUTORIAL A*: PART 1                                                                                      | SITZUNG 1    |  |

|--------------------------------------------------------------------------------------------------------------------------------|--------------|--|

| Analog, Mixed-Signal, RF IC Testing: Essentials and Cu                                                                         | rrent Trends |  |

| Harlampos STRATIGOPOULOS, Sorbonne University - Ll                                                                             |              |  |

| 14:00 - 16:00 TSS@ETS TUTORIAL B*: PART 1                                                                                      | SITZUNG 7/8  |  |

| <b>System-Level Test</b><br>Harry CHEN <i>, MediaTek - TW</i>                                                                  |              |  |

| 16:00 - 16:30 Coffee Break                                                                                                     | FOYER        |  |

|                                                                                                                                |              |  |

| 16:30 - 18:30 TSS@ETS TUTORIAL A*: PART 2                                                                                      | SITZUNG 1    |  |

| Analog, Mixed-Signal, RF IC Testing: Essentials and Current Trends<br>Harlampos STRATIGOPOULOS, Sorbonne University - LIP6, FR |              |  |

| 16:30 - 18:30 TSS@ETS TUTORIAL B*: PART 2                                                                                      | SITZUNG 7/8  |  |

| System-Level Test<br>Harry CHEN, MediaTek - TW                                                                                 |              |  |

| 18:30 - 19:00 Break                                                                                                            | FOYER        |  |

|                                                                                                                                |              |  |

| 19:00 - 21:00 Welcome Reception                                                                                                |              |  |

|                                                                                                                                | KURHAUS      |  |

\*The TSS@ETS Tutorials of Monday afternoon are accessible to all ETS attendees with a full registration.

## TUESDAY, MAY 28, 2019

9:30 - 10:15 SESSION 1 - KEYNOTE 1

9:00 - 9:30 OPENING SESSION Opening Ceremony Awards

| 9.50 - 10.15 SESSION 1 - RETNOTE 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | KOINGRESS T                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Moderator: Mehdi TAHOORI, <i>KIT - DE</i><br>Cognitive Computing: Design, Verification & Security<br>Kaushik ROY, Purdue University - US                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Challenges                                                      |

| 10:15 - 11:00 Coffee Break                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FOYER                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                 |

| 10:00 - 11:00 POSTER SESSION 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FOYER                                                           |

| On the Evaluation of the PIPB Effect within SRAM-base<br>Corrado DE SIO, Sarah AZIMI, Luca STERPONE, Politecnic<br>B-open: A New Defect in Nanometric Technologies due<br>Process<br>Freddy FORERO <sup>1</sup> , Michel RENOVELL <sup>2</sup> , Victor CHAMPAC <sup>1</sup><br><sup>1</sup> /INAOE - MX, <sup>2</sup> LIRMM - FR<br>Test Solutions for High Density 3D-IC Interconnects - For<br>on-Logic Partitioning<br>Imed JANI, Pascal VIVET, Jean DURUPT, Sebastien THURI<br>Didier LATTARD, Edith BEIGNE, <i>CEA-LETI - FR</i><br>Feature Engineering for Recycled FPGA Detection Bases<br>Variation Modeling<br>Foisal AHMED, Michihiro SHINTANI, Michiko INOUE<br>Nara Institute of Science and Technology (NAIST) - JP<br>DFT Scheme for Hard-to-Detect Faults in FinFET SRAMS<br>Guilherme Cardoso MEDEIROS <sup>1</sup> , Mottaqiallah TAOUIL <sup>1</sup> ,<br>Moritz FIEBACK <sup>1</sup> , Leticia Bolzani POEHLS <sup>2</sup> , Said HAMDIOU<br><sup>1</sup> Delft University of Technology - NL,<br><sup>2</sup> Catholic University of Rio Grande do Sul - BR | e di Torino - IT<br>to SADP<br>ocus on SRAM-<br>ES,<br>d on WID |

KONGRESS 1

KONGRESS 1

## 11:00 - 12:30 SESSION 2A: Security KONGRESS 1 Moderators: Subhasish MITRA, Stanford University - US Johanna SEPULVEDA, TUM - DE Inter-Lock: Logic Encryption for Processor Cores Beyond Module Boundaries Dominik SISEJKOVIC<sup>1</sup>, Farhad MERCHANT<sup>1</sup>, Rainer LEUPERS<sup>1</sup>, Gerd ASCHEID<sup>1</sup>, Sascha KEGREISS<sup>2</sup> <sup>1</sup>RWTH Aachen - DE, <sup>2</sup>Hensoldt Cyber GmbH - DE On Integrating Lightweight Encryption in Reconfigurable Scan Networks Benjamin THIEMANN<sup>1</sup>, Linus Feiten<sup>1</sup>, Pascal RAIOLA<sup>1</sup>, Bernd BECKER<sup>1</sup>, Matthias SAUER<sup>2</sup>

<sup>1</sup>University of Freiburg - DE, <sup>2</sup>Advantest - DE **Revisiting Logic Locking for Reversible Computing** Nimisha LIMAYE, Muhammad YASIN, Ozgur SINANOGLU New York University Abu Dhabi - AE

11:00 - 12:30 SESSION 2B: Analog and Mixed Signal Test SITZUNG 1

Moderators: Hans KERKHOFF, University of Twente -NL Haralampos STRATIGOPOULOS, Sorbonne University - LIP6 - FR

A 52 dB-SFDR 166 MHz Sinusoidal Signal Generator for Mixed-Signal BIST Applications in 28 nm FDSOI technology Hani MALLOUG, Manuel BARRAGAN, Salvador MIR, TIMA - FR

Power Measurement and Spectral Test of ZigBee Transmitters from

1-bit Under-sampled Acquisition Thibault VAYSSADE<sup>1</sup>, Florence AZAÏS<sup>2</sup>, Laurent LATORRE<sup>2</sup>, Francois LEFEVRE<sup>1</sup>, <sup>1</sup>NXP - FR, <sup>2</sup>LIRMM - FR

Model-driven AMS Test Setup Validation Tool Prepared for IEEE P1687.2 Leon VAN DE LOGT<sup>1</sup>, Vladimir ZIVKOVIC<sup>2</sup>, Ingrid VAN BAAST<sup>1</sup>

<sup>1</sup>D4T Systems - NL, <sup>2</sup>Cadence - UK 24<sup>th</sup> IEEE European Test Symposium 2019 – Program at a Glance

#### 26

## TUESDAY, MAY 28, 2019

| 11:00 - 12:3 | D SESSION 2C: ETS <sup>2</sup>               | SITZUNG 7/8  |

|--------------|----------------------------------------------|--------------|

|              | Functional Safety and DFT –                  |              |

|              | Overlap or Conflict?                         |              |

| Moderators   | Pete HARROD, ARM - UK                        |              |

|              | Zebo PENG, Linkoping University - SE         |              |

| Presenters:  | Teresa MCLAURIN <i>, ARM - US</i>            |              |

|              | Jan SCHAT, NXP Semiconductors - DE           |              |

|              | Michael SCHREINER, Infineon - DE             |              |

|              |                                              |              |

| 12.20 14.0   |                                              |              |

| 12:30 - 14:0 | 0 Lunch Break                                | PARKPAVILLON |

| 14.00 15.0   |                                              | KONCDECC 4   |

| 14:00 - 15:3 | 0 SPECIAL SESSION 3A:                        | KONGRESS 1   |

|              | Maintaining Automotive Quality for           |              |

| <b>a</b> .   | Next Generation Microcontrollers             |              |

| Organizer ar | nd Moderator: Daniel TILLE, Infineon Techn   | ologies - DE |

|              |                                              |              |

| Presenters:  |                                              |              |

|              | ITOVTCHENKO, Synopsys - DE                   |              |

|              | DLD, Infineon Technologies - DE              |              |

| Johanna S    | EPULVEDA, TU-Munich - DE                     |              |

|              |                                              |              |

| 14:00 - 15:3 | 0 SESSION 3B: McCluskey                      | SITZUNG 1    |

|              | Doctoral Thesis Award – ETS Semi-Finals      |              |

| Moderators   | : Alberto BOSIO, École Centrale de Lyon - FR |              |

|              |                                              |              |

15:30 - 16:15 Coffee Break

Said HAMDIOUI, TU Delft - NL

FOYER

#### 15:30 - 16:15 PhD Forum FOYER A Methodology for Characterization and Mitigation of SET Effects in **Combinational Logic** Marko ANDJELKOVIC, Milos KRSTIC, Rolf KRÄMER, IHP - DE Programmable In-Situ Delay Monitor for Energy-Efficient and Resilient Complex SoC Mitko VELESKI, Rolf KRÄMER, Milos KRSTIC, IHP - DE Dependability of Safety-Critical Automotive SoC Marco RESTIFO, Politecnico di Torino - IT A boot-time self-test procedures scheduler for multi-core automotive System-on-Chips Andrea FLORIDIA, Politecnico di Torino - IT Self-Adaptive Cross-Layer Fault Tolerance in Multiprocessor Systems Junchao CHEN, Milos KRSTIC, IHP - DE SAT modulo differential equations Tomas KOLARIK, Stefan RATSCHAN, CTU Prague - CZ **Encryption Techniques for Test Infrastructures** Emanuele VALEA<sup>1</sup>, Marie-Lise FLOTTES<sup>1</sup>, Giorgio DI NATALE<sup>2</sup>, Bruno ROUZEYRE<sup>1</sup>, <sup>1</sup>LIRMM - FR, <sup>2</sup>TIMA - FR On the Evaluation of SET-induced Errors on **Dynamically Reconfigurable FPGAs** Corrado DE SIO, Ludovica BOZZOLI, Sarah AZIMI, Luca STERPONE Politecnico di Torino - IT Verifying IEEE 1687 ICL against RTL -**Code Coverage and Functional Coverage** Aleksa DAMLJANOVIC, Politecnico di Torino - IT Efficient hardening solutions on GPUs for safety critical applications Fernando Fernandes DOS SANTOS. Paolo RECH Universidade Federal do Rio Grande do Sul - BR Embedded System back-annotation by qualifying component model template Katayoon BASHARKHAH, University of Tehran - IR Machine Learning to Tackle the Challenges of **Transient and Soft Errors in Complex Circuits** Thomas LANGE<sup>1</sup>, Aneesh BALAKRISHNAN<sup>1</sup>, Maximilien GLORIEUX<sup>1</sup>, Dan ALEXANDRESCU<sup>1</sup>, Luca STERPONE<sup>2</sup> <sup>1</sup>iRoC Technologies, <sup>2</sup>Politecnico di Torino - IT Learning Enhanced Diagnosis of Logic Circuit Failures Soumya MITTAL, Shawn BLANTON, Carnegie Mellon University - US Vector-IR-based translation approach of pattern programs Jung-Geun PARK, Minsu KIM, Seoul National University - KR

## TUESDAY, MAY 28, 2019

**KONGRESS 1** 16:15 - 17:45 SESSION 4A: Test Generation Moderators: Grzegorz MRUGALSKI, Mentor, a Siemens Business - PL Melanie SCHILLINSKY, NXP - DE Machine Learning-based Prediction of Test Power Harshad DHOTRE<sup>1</sup>, Stephan EGGERSGLUESS<sup>2</sup>, Krishnendu CHAKRABARTY<sup>3</sup>, Rolf DRECHSLER<sup>1</sup> <sup>1</sup>University of Bremen - DE, <sup>2</sup>Mentor, a Siemens Business - DE, <sup>3</sup>Duke University - US On Generating Fault Diagnosis Patterns for Designs with X Sources Xijiang LIN<sup>1</sup>, Sudhakar REDDY<sup>2</sup> <sup>1</sup>Mentor, a Siemens Business - US, <sup>2</sup>University of Iowa - US High-Level Combined Deterministic and Pseudoexhaustive Test Generation for RISC Processors Adeboye OYENIRAN, Raimund UBAR, Maksim JENIHHIN, Cemil Cem GURSOY, Jaan RAIK, Tallinn University of Technology - EE 16:15 - 17:45 SESSION 4B: Fault Tolerance SITZUNG 1 Moderators: Valentin GHERMAN, CEA - FR Huang ZHENGFENG, Hefei University of Technology - CN IJTAG Compatible Timing Monitor with Robust Self-Calibration for **Environmental and Aging Variations** Ghazanfar ALI, Jerrin PATHROSE, Hans KERKHOFF University of Twente - NL STAHL: A Novel Scan-Test-Aware Hardened Latch Design Ruijun MA<sup>1</sup>, Stefan HOLST<sup>1</sup>, Xiaoqing WEN<sup>1</sup>, Aibin YAN<sup>2</sup>, Hui XU<sup>2</sup> <sup>1</sup>Kyushu Institute of Technology - JP, <sup>2</sup>Anhui University - CN Hardware-Based Aging Mitigation Scheme for Memory Address Decoder Daniel KRAAK<sup>1</sup>, Innocent AGBO<sup>1</sup>, Mottagiallah TAOUIL<sup>1</sup>, Said HAM-DIOUI<sup>1</sup>, Pieter WECKX<sup>2</sup>, Stefan COSEMANS<sup>2</sup>, Francky CATTHOOR<sup>2</sup> <sup>1</sup>Delft University of Technology - NL, <sup>2</sup>IMEC - BE 17:45 - 18:00 Break FOYER 18:00 - 19:30 SESSION 5: Wine and Cheese Panel **KONGRESS 1** Organizer and Moderator: Jeff REARICK, AMD - US The Test Industry Roadmap: Ask the Experts!

For more information see page 16.

## 19:30 - 21:30 Networking Grill

For more information see page 42.

PARKPAVILLON

## WEDNESDAY, MAY 29, 2019

| 8:30 - 9:15 SESSION 6: Keynote 2                                                                 | KONGRESS 1         |

|--------------------------------------------------------------------------------------------------|--------------------|

| Moderator: Krishnendu CHAKRABARTY, Duke University -                                             | US                 |

| Software Defined Chips: An Innovative Architecture Le                                            | eading to          |

| Intelligent Computing                                                                            |                    |

| Shaojun WEI, Tsinghua University - CN                                                            |                    |

|                                                                                                  |                    |

| 9:15 - 10:15 SESSION 7A: Memory                                                                  | KONGRESS 1         |

| Moderators: Michele STUCCHI, IME - BE                                                            |                    |

| Ioana VATAJELU, <i>TIMA - FR</i>                                                                 |                    |

| Pinhole Defect Characterization and Modeling for STT-                                            | MRAM               |

| Testing                                                                                          |                    |

| Lizhou WU <sup>12</sup> , Siddharth RAO <sup>2</sup> , Guilherme Cardoso MED                     | FIROS <sup>1</sup> |

| Mottaqiallah TAOUIL <sup>1</sup> , Erik Jan MARINISSEN <sup>2</sup> , Farrukh Y                  |                    |

| Sebastien COUET <sup>2</sup> , Said HAMDIOUI <sup>1</sup> , Gouri Sankar KAR <sup>2</sup>        |                    |

| <sup>1</sup> Delft University of Technology - NL, <sup>2</sup> IMEC - BE                         |                    |

| A Machine Learning based Approach to Optimize Repa                                               | air of Embod       |

| ded Flash Memories in Automotive System-on-Chip                                                  | an of Embeu-       |

| Andrea MANZINI <sup>13</sup> , Pietro INGLESE <sup>24</sup> , Leonardo CALDI <sup>4</sup> ,      |                    |

|                                                                                                  |                    |

| Riccardo CANTORO <sup>2</sup> , Giambattista CARNEVALE <sup>3</sup> ,                            | ONE3               |

| Matteo COPPETTA <sup>3</sup> , Massimo GILTRELLI <sup>3</sup> , Nellina MAUT                     |                    |

| Fernanda IRRERA <sup>1</sup> , Rudolf ULLMANN <sup>4</sup> , Paolo BERNARDI                      | -                  |

| <sup>1</sup> University of Rome - IT, <sup>2</sup> Politecnico di Torino - IT,                   |                    |

| ³Infineon - IT, ⁴Infineon - DE                                                                   |                    |

| 0.45 40.45 CECCION 7D. Mandau Cassian                                                            |                    |

| 9:15 - 10:15 SESSION 7B: Vendor Session                                                          | SITZUNG 7/8        |

| Moderator: Hans MANHAEVE, Ridgetop Europe - BE                                                   |                    |

| Test and Repair for SoC Memories and Hierarchical Tes                                            | st for             |

| AMS & PHY IP                                                                                     |                    |

| Yervant ZORIAN, Synopsys Fellow - US                                                             |                    |

| Advantest and EDA: Partnering to Deliver Customer Va                                             | alues              |

| Michael BRAUN, Advantest - DE                                                                    |                    |

|                                                                                                  |                    |

| 9:15 - 10:15 SESSION 7C: Embedded Workshop:                                                      | SITZUNG 1          |

| Case Studies                                                                                     |                    |

| Moderator: Gildas LEGER, IMSE-CNM - ES                                                           |                    |

| Flight Safety Certification Implications for Complex Mu                                          | ulti-Core          |

| Processor based Avionics Systems                                                                 |                    |

| Jyotika ATHAVALE <sup>1</sup> , Riccardo MARIANI <sup>2</sup> , Michael PAULIT                   | SCH <sup>3</sup>   |

| <sup>1</sup> Intel Corporation - US, <sup>2</sup> Intel Corporation - IT, <sup>3</sup> Intel Cor | poration - DE      |

| Hybrid Verification Methodology for Automotive RAD                                               | AR                 |

| Shiva NEGENDAR, Sainath KARLAPALEM, Paulraj KANAK                                                | (ARAJ, Shas-       |

| hank VENUGOPAL, NXP - IN                                                                         |                    |

|                                                                                                  |                    |

## WEDNESDAY, MAY 30, 2018

| 10:15 - 11:00 Coffee Break                                                                                             | FOYER                  |

|------------------------------------------------------------------------------------------------------------------------|------------------------|

|                                                                                                                        |                        |

| 10:15 - 11:00 POSTER SESSION 2                                                                                         | FOYER                  |

| Concurrent Estimation of a PLL Transfer Function by                                                                    |                        |

| Cross-Correlation with pseudo-random Jitter                                                                            |                        |

| Jan SCHAT, Ulrich MÖHLMANN, NXP Semiconductors - D                                                                     | E                      |

| PaTran: a Translation Platform for Test Pattern Program                                                                |                        |

| Jung-Geun PARK <sup>1</sup> , Minsu KIM <sup>1</sup> , Sungyeol KIM <sup>2</sup> , Insu YANG                           | 5 <sup>2</sup> ,       |

| Hyunsoo JUNG <sup>2</sup> , Soo-Mook MOON <sup>2</sup>                                                                 |                        |

| <sup>1</sup> Seoul National University - KR, <sup>2</sup> Samsung Electronics Co.                                      | ., Ltd KR              |

| A Functional Approach to Test and Debug of IEEE 1687                                                                   |                        |

| Reconfigurable Networks                                                                                                | 2                      |

| Michele PORTOLAN <sup>1</sup> , Riccardo CANTORO <sup>2</sup> , Ernesto SANC                                           | CHEZ <sup>2</sup>      |

| <sup>1</sup> TIMA - FR, <sup>2</sup> Politecnico di Torino - IT                                                        |                        |

| Test Adapted Shielding by a Multipurpose Crosstalk                                                                     |                        |

| Avoidance Scheme                                                                                                       |                        |

| Mahsa AKHSHAM, Atefesadat SEYEDOLHOSSEINI,                                                                             |                        |

| Zainalabedin NAVABI, University of Tehran - IR                                                                         | D                      |

| Hybrid Architecture for Embedded Test Compression to                                                                   | Process                |

| <b>Rejected Test Patterns</b><br>Sebastian HUHN <sup>1</sup> , Daniel TILLE <sup>2</sup> , Rolf DRECHSLER <sup>3</sup> |                        |

| <sup>1</sup> DFKI GmbH - DE, <sup>2</sup> Infineon - DE, <sup>3</sup> University of Bremen/L                           |                        |

| DERI GIIDE - DE, IIIJIIEOII - DE, OIIIVEISILY OJ BIEIIEIJE                                                             | DFKI - DE              |

|                                                                                                                        |                        |

| 11:00 - 12:30 SESSION 8A: Modeling, Validation                                                                         | KONGRESS 1             |

| and Verification                                                                                                       |                        |

| Moderators: Bernd BECKER, University of Freiburg - DE                                                                  |                        |

| René KRENZ-BAATH, Hamm-Lippstadt Univ                                                                                  | ersity of              |

| Applied Sciences - DE                                                                                                  | , ,                    |

| Back-Annotation of Interconnect Physical Properties                                                                    | for System-            |

| Level Crosstalk Modeling                                                                                               | -                      |

| Zainalabedin NAVABI, Rezgar SADEGHI, Nooshin NOSF                                                                      | RATI,                  |

| Katayoon BASHARKHAH, University of Tehran - IR                                                                         |                        |

| Post-Silicon Validation of IEEE 1687 Reconfigurable Scan Networks                                                      |                        |

| Aleksa DAMLJANOVIC <sup>1</sup> , Artur JUTMAN <sup>2</sup> , Giovanni SQU                                             | IILLERO <sup>1</sup> , |

| Anton TSERTOV <sup>2</sup> , <sup>1</sup> Politecnico di Torino - IT, <sup>2</sup> Testonica                           | Lab - EE               |

| Exploring Algebraic Interpolants for Rectification of F                                                                | inite Field            |

| Arithmetic Circuits with Groebner Bases                                                                                |                        |

| Utkarsh GUPTA <sup>1</sup> , Priyank KALLA <sup>2</sup> , Irina ILIOAEA <sup>2</sup> , Floria                          | n ENESCU <sup>2</sup>  |

| <sup>1</sup> University of Utah - US, <sup>2</sup> Georgia State University - US                                       | 5                      |

|                                                                                                                        |                        |

Home of the unmatched **Q-Star Test** current measurement instruments serving quality assurance and test cost reduction, the **ProChek Plus** device characterization platform and Ridgetop's solutions serving predictive diagnosis.

Learn more about our Innovations and Solutions in Test, Measurement and Predictive Diagnosis at **www.ridgetop.eu**

Theater

## WEDNESDAY, MAY 30, 2018

| 11:00 - 12:30 SPECIAL SESSION 8B:                                                                                                                | SITZUNG 7/8    |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Security in Autonomous Systems                                                                                                                   |                |

| Organizer and Moderator: Ilia POLIAN, University of Stut                                                                                         | tgart - DE     |

| Presenters:<br>Francesco REGAZZONI, University of Lugano - CH<br>Marc STÖTTINGER, Continental AG - DE<br>Stefan KATZENBEISSER, TU-Darmstadt - DE |                |

| 11:00 - 12:30 SESSION 8C: Embedded Workshop:                                                                                                     | SITZUNG 1      |

| Advances in DfT                                                                                                                                  |                |

| Moderators: Jochen Rivoir, Advantest - DE                                                                                                        |                |

| Matthias Sauer, Advantest - DE                                                                                                                   |                |

| Architecture for fast and precise and Voltage Measur                                                                                             | rement for     |

| Analog Test Points                                                                                                                               |                |

| Jan Schat, NXP Semiconductors - DE                                                                                                               |                |

| Facilitating Memory Test Using Shared Bus Interface                                                                                              |                |

| Albert AU <sup>1</sup> , Sebastian BROMBEREK <sup>2</sup> , Martin KEIM <sup>3</sup> ,                                                           |                |

| Benoit NADEAU-DOSTIE <sup>1</sup> , Artur POGIEL <sup>2</sup>                                                                                    |                |

| <sup>1</sup> Mentor, a Siemens Business - CA, <sup>2</sup> Mentor, a Siemens                                                                     | Business - PL, |

| <sup>3</sup> Mentor, a Siemens Business - US                                                                                                     |                |

| Novel Clock and Reset DFT Methods to Improve Hier                                                                                                | archical ATPG  |

| Pattern Reuse Shown on a GPU Design                                                                                                              |                |

| Beomseok SHIN <sup>2</sup> , Jinsoo PARK <sup>2</sup> , Jungyul PYO <sup>2</sup> , Youngm                                                        | nin SHIN²,     |

| Ron PRESS <sup>1</sup> , Takeo KOBAYASHI <sup>1</sup> , Yoon Dong LEE <sup>3</sup> , Inchu                                                       | ıl KIM³        |

| <sup>1</sup> Mentor, a Siemens Business - US, <sup>2</sup> Samsung Electronic                                                                    | cs - KR,       |

| <sup>3</sup> Mentor, a Siemens Business - KR                                                                                                     |                |

12:30 - 14:00 Lunch Break

Geroldsauer Mühle

PARKPAVILLON

SITZUNG 7/8

14:00 - 15:30 SESSION 9A: Panel System-level Test (SLT) -What does the Future Hold? Organizer: Harry Chen, MediaTek - TW

Panelists: John YI, AMD - US Marc HUTNER, Teradyne - CA Anil BHALLA, Advantest - US Carsten OHLHOFF, Continental Automotive - DE Adit SINGH, Auburn University - US Paolo BERNARDI, Politecnico di Torino - IT

For more information see page 16

14:00 - 15:00 SESSION 9B: Embedded Tutorial: Alternatives to Fault Injections for Early Safety/Security Evaluations Organizer and Moderator: Régis LEVEUGLE, *TIMA - FR*

SITZUNG 1

Presenters:

Régis LEVEUGLE, *TIMA - FR* Michele PORTOLAN, *TIMA - FR* Stefano DI CARLO, *Politecnico di Torino - IT*

15:30 - 16:30 Break

16:30 - 22:00 Social Event See page 42 for more information. ENTRANCE

## THURSDAY, MAY 30, 2019

| 8:30 - 9:15 SESSION 10: Keynote 3<br>Moderator: Hans-Joachim WUNDERLICH, University of S<br>Hold the reins in test engineering<br>Jochen Müller, Bosch - DE                                                                                                                                                                                                                                                                                                                                                                                                                                         | KONGRESS 1<br>tuttgart - DE |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 9:15 - 10:15 SESSION 11A: Approximate and<br>Neuromorphic Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | KONGRESS 1                  |

| Moderators: Rohit KAPUR, <i>Cadence - US</i><br>Adit SINGH, <i>Auburn University - US</i><br><b>Approximate computing design exploration</b><br><b>through data lifetime metrics</b><br>Alessandro SAVINO <sup>1</sup> , Michele PORTOLAN <sup>2</sup> , Régis LEVEI<br>Stefano DI CARLO <sup>1</sup> , <i>Politecnico di Torino - IT</i> , <sup>2</sup> TIMA - F<br><b>Impact of Reduced Precision in the Reliability of</b><br><b>Deep Neural Networks for Object Detection</b><br>Fernando Fernandes DOS SANTOS, Philippe NAVAUX,<br>Paolo RECH, <i>Universidade Federal do Rio Grande do Su</i> | R<br>Luigi CARRO,           |

| 8:30 - 9:15 SESSION 11B: Vendor Session<br>Moderator: Pete HARROD, <i>ARM - UK</i><br>Mini-Tutorial: <b>The (black) art of current test</b><br>Hans Manhaeve, <i>CEO Ridgetop Europe - BE</i>                                                                                                                                                                                                                                                                                                                                                                                                       | SITZUNG 7/8                 |

| 8:30 - 9:15 SESSION 11c: Embedded Tutorial:<br>Connecting the Dots: How IEEE P1687.1,<br>P1687.2, and IEEE P2427 Play Together<br>Organizer: Martin KEIM, <i>Mentor, a Siemens Business</i> -                                                                                                                                                                                                                                                                                                                                                                                                       | SITZUNG 1                   |

| Moderator: Jeff REARICK, AMD - US Presenters:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |

| Martin KEIM, <i>Mentor, a Siemens Business - US</i><br>Jeff REARICK, <i>AMD - US</i><br>Vladimir ZIVKOVIC, <i>Cadence - UK</i><br>10:15 - 11:00 Coffee Break                                                                                                                                                                                                                                                                                                                                                                                                                                        | FOYER                       |

#### 35

| Symbolic Circuit Analysis under an Arc Based Timing Model                                           |  |  |

|-----------------------------------------------------------------------------------------------------|--|--|

| Goerschwin FEY <sup>1</sup> , Alberto GARCIA-ORTIZ <sup>2</sup>                                     |  |  |

| <sup>1</sup> TU Hamburg - DE, <sup>2</sup> University of Bremen - DE                                |  |  |

| A Dynamic Greedy Test Scheduler for Optimizing                                                      |  |  |

| Probe Motion in In-Circuit Testers                                                                  |  |  |

| Matteo Sonza Reorda <sup>1</sup> , Giovanni Squillero <sup>1</sup> , Luciano Bonaria <sup>2</sup> , |  |  |

| Maurizio Raganato <sup>2</sup> , <sup>1</sup> Politecnico di Torino - IT, <sup>2</sup> SPEA - IT    |  |  |

|                                                                                                     |  |  |

| 11:00 - 12:30 SESSION 12A: DfT and BIST KONGRESS 1                                                  |  |  |

| for 3D and AMS                                                                                      |  |  |

| Moderators: Jürgen ALT, Intel - DE                                                                  |  |  |

| Erik Jan MARINISSEN <i>, IMEC - BE</i>                                                              |  |  |

| Digital Built-in Self-Test for Phased Locked Loops to                                               |  |  |

| Enable Fault Detection                                                                              |  |  |

| Mehmet INCE, Sule OZEV, Arizona State University - US                                               |  |  |

| Built-in Self-Test for Inter-Layer Vias in Monolithic 3D ICs                                        |  |  |

| Arjun CHAUDHURI <sup>1</sup> , Sanmitra BANERJEE <sup>1</sup> , Heechun PARK <sup>2</sup> ,         |  |  |

| Bon Woong KU <sup>2</sup> , Krishnendu CHAKRABARTY <sup>1</sup> , Sung Kyu LIM <sup>2</sup>         |  |  |

| <sup>1</sup> Duke University - US, <sup>2</sup> Georgia Institute of Technology - US                |  |  |

| K^3 TAM Optimization for Testing 3D-SoCs using Non-Regular                                          |  |  |

| Time-Division-Multiplexing                                                                          |  |  |

| Panagiotis GEORGIOU, lakovos THEODOSOPOULOS,                                                        |  |  |

| Chrysovalantis KAVOUSIANOS, University of Ioannina - GR                                             |  |  |

|                                                                                                     |  |  |

| 11:00-12:30 Session 12B – Vendor Session SITZUNG 7/8                                                |  |  |

| Moderator: Jürgen SCHLÖFFEL, Mentor, a Siemens Business - DE                                        |  |  |

| Moving DFT solutions to the next level                                                              |  |  |

| Kan THAPAR, Mentor, a Siemens Business - UK                                                         |  |  |

| IP Solutions for Functional Safety Applications                                                     |  |  |

| Pete HARROD, Director of Functional Safety, CPU Group, ARM - UK                                     |  |  |

| ProChak Plus A solution for Process assessment from a quality/                                      |  |  |

Test Pattern Generator for Majority Voter based QCA **Combinational Circuits targeting MMC Defect** Vaishali DHARE, Usha MEHTA, Nirma University - IN S G 17

10:15 - 11:00 POSTER SESSION 3

## Α Ρ

s - DE N ARM - UK ProChek Plus – A solution for Process assessment from a quality/ reliability perspective Hans MANHAEVE, CEO Ridgetop Europe - BE

#### FOYER

# **THURSDAY, MAY 30, 2019**

11:00 - 12:30 SPECIAL SESSION 12C: Dependable Wireless Industrial IoT

Organizers: Fotis FOUKALAS and Paul POP, TU-Denmark - DK Moderator: Fotis FOUKALAS, TU-Denmark - DK

#### Presenters:

Fabrice THEOLEYRE, CNRS - FR Carlo Alberto BOANO. TU-Graz - AT Chiara BURATTI, University of Bologna - IT Fotis FOUKALAS, TU-Denmark - DK

#### 12:30 - 14:00 Lunch Break

**KONGRESS 1** 14:00 - 15:30 SESSION 13: Diagnosis Moderators: Sybille HELLEBRAND, University of Paderborn - DE Stefan HOLST, Kyushu Institute of Technology - JP A Supervised Machine Learning Application in Volume Diagnosis Yue TIAN<sup>1</sup>, Gaurav VEDA<sup>2</sup>, Wu-Tung CHENG<sup>2</sup>, Manish SHARMA<sup>2</sup>, Huaxing TANG<sup>2</sup>, Neerja BAWASKAR<sup>3</sup>, Sudhakar REDDY<sup>1</sup> <sup>1</sup>University of Iowa - US, <sup>2</sup>Mentor, a Siemens Business - US, <sup>3</sup>Globalfoundries - US Non-Adaptive Pattern Reordering to Improve Scan Chain Diagnostic Resolution Yu HUANG, Jakub JANICKI, Szczepan URBAN Mentor, a Siemens Business - US LearnX: A Hybrid Deterministic-Statistical Defect Diagnosis Methodology Soumya Mittal, Shawn Blanton, Carnegie Mellon University - US

15:30 - 16:00 CLOSING SESSION

18:00 - 19:00 Workshop Reception See page 38 for more information. SITZUNG 1

PARKPAVILLON

**KONGRESS 1**

FOYER

Stadtmuseum

# Festspielhaus

# CADENCE MODUS DFT SOFTWARE SOLUTION

# QUALITY • RELIABILITY • SAFETY

www.cadence.com/modus

cādence

© 2019 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at www.cadence.com/go/trademark are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners.

# **FRINGE Workshops**

The following workshops are co-located with ETS'19 and will run in parallel, starting Thursday May 30 at 16:00, ending Friday May 31 at 15:30/18:00. There will be a workshop reception for the workshop attendees on Thursday May 30 at 18:00, which takes places in 1st floor Foyer between SITZUNG 1 and SITZUNG 4.

#### **TESTA'19**

4th International Test Standards Application Workshop

General Chair: Michele PORTOLAN, TIMA - Grenoble, FR

Room: SITZUNG 4

The TESTA workshop is a focused, open discussion platform dedicated to exchange of fresh ideas, industrial best practices, methodologies and work-in-progress around test related standards, especially those being actively developed today or the ones recently released. Contributions covering IEEE 1149.x, IEEE 1500, IEEE 1687, IEEE 1450, and open Working Groups like IEEE P1838, IEEE P1687.x and STAM are expected. Particularly welcome are contributions that discuss what works, what does not, or how the standards were incorporated into existing or new DFT methodologies. Reports on first-time usage of new and upcoming standards are welcome, as is research exploring the best usage of features described in these standards.

Further Information:

https://www.testgroup.polito.it/ets19/testa2019/

### SHIVA:

Secure Hardware, Integrity and preVention of Attacks Workshop

#### Organizers:

Hans-Joachim WUNDERLICH, University of Stuttgart - DE Bernd BECKER, University of Freiburg - DE

Room: SITZUNG 1

The SHIVA Workshop will provide an environment for researchers and practitioners from academia and industry as well to discuss challenges, recent developments, and on-going work in hardware security, in particular w.r.t. topics like securing scan infrastructure against attacks, techniques to protect a system against (un)intentional manipulation and against reading out of confidential information or intellectual property.

Further Information:

http://www.iti.uni-stuttgart.de/ lehre/ets-workshop-2019.html

## **TRUDEVICE 2019**

8<sup>th</sup> Workshop on Trustworthy Manufacturing and Utilization of Secure Devices

General Chairs: Francesco REGAZZONI, ALaRI - USI - CH Giorgio DI NATALE, CNRS - TIMA - Grenoble, FR

Program Chairs: Osnat KEREN, Bar Ilan University - IL Stjepan PICEK, Delft University of Technology - NL

Room: SITZUNG 1

Hardware security is becoming increasingly important for many embedded systems applications ranging from small RFID tag to satellites orbiting the earth: secure applications such as public services, communication, control and healthcare keep growing, however hardware devices that implement cryptography functions has become the Achille's heel in the last decade. The TRUDEVICE Workshop will provide an environment for researchers from academic and industrial domains who want to discuss recent findings, theories and on-going work on all aspects of hardware security including design, manufacturing, testing, reliability, validation and utilization. Program will include invited talks, contributed talks and work in progress.

Further Information:

https://www.testgroup.polito.it/ets19/ trudevice-workshop-call-for-contributions

# **FRINGE Meetings**

#### **ETS Steering Committee Meeting**

Chair: Matteo SONZA REORDA Room: SITZUNG 4 Monday, May 27, 16:00–19:00

#### **ETS Steering Committee Meeting**

Chair: Matteo SONZA REORDA Room: SITZUNG 4 Tuesday, May 28, 12:30–14:00

#### ETTTC Meeting

Chair: Alberto BOSIO Room: SITZUNG 4 Wednesday, May 29, 12:30–13:30

About eTTTC:

The European Test Technology Technical Council (eTTTC) is the European section of the TTTC. eTTTC is a volunteer professional organization sponsored by the IEEE Computer Society.

TTTC's goals are to contribute to our members' professional development and advancement, to help them solve engineering problems in electronic test, and to help advance the state-of-the art.

This meeting provides all actors involved in test technology to share information on upcoming events and projects.

#### **ETS2020 Executive Committee Meeting**

Chairs: Artur JUTMAN and Jaan RAIK Room: SITZUNG 4 Thursday, May 30, 12:30–14:00

# **Welcome Reception**

The welcome reception of ETS 2019 takes place at Kurhaus Baden-Baden, next to the casino and overlooking the historical Trinkhalle. It is close to the conference venue, reachable in only five minutes by foot.

See the map on page 46/47 for the location.

The event will take place on Monday, May 27th, 2019 starting at 19:00.

Kurhaus Baden-Baden Kaiserallee 1 D-76530 Baden-Baden

# **Networking Grill**

After the panel discussion on Tuesday afternoon, all conference attendees are invited for a networking grill on the terrace of Parkpavillon (conference venue) for a get-together and networking with good food and drinks.

The event will take place on Tuesday, May 28th, 2019 starting at 19:30.

Baden-Baden Kur&Tourismus GmbH

# TEST FOR THE AUTONOMOUS AGE

Ille

2)))

ኈ

Π

Mentor's Tessent product line is the technology and market leading design-for-test solution. Tessent's RTL-based hierarchical DFT solution enables customers to achieve lower test cost, higher test quality, faster yield ramps and meet the functional safety requirements demanded by the automotive market's ISO 26262 standard.

Mentor, a Siemens business, is a proud sponsor of the 2019 European Test Symposium

# **Social Activities**

The main social event will be on Wednesday, May 29. This year's social event starts at 16:30 in front of the conference venue with a guided tour through Baden-Baden. Afterwards we will go to Geroldsauer Mühle by bus and spend the rest of the evening there. The departure of the buses will be at 18:30 in front of the venue entrance.

#### 16:30 - 18:30 Guided walking tour of Baden-Baden

Discover Baden-Baden on this guided walking tour with the certified city guides and stroll through the elegant "Kurviertel" with its magnificent buildings like the "Kurhaus/Casino", the Theater and the "Trinkhalle" (Pump Room). Furthermore, you will get to know the traditional "Spa Quarter" and the historic "Old Town" of Baden-Baden as well as interesting facts and anecdotes.

Meeting point: 4.30 p.m., in front of the entrance of the Kongresshaus Baden-Baden (Augustaplatz 10).

English-speaking Baden-Baden guides will be waiting for you.

Duration of the walking tour: 1.5 – 2 hours

Trinkhalle

Brahmshaus

Casino

All images by Baden-Baden Kur & Tourismus GmbH

#### 18:30 - 22:00 Geroldsauer Mühle

As gate to the Black Forest, the Geroldsauer Mühle (mill) is known thanks to its geographical location, as well as thanks to its offer to experience the Black Forest in its purest form.