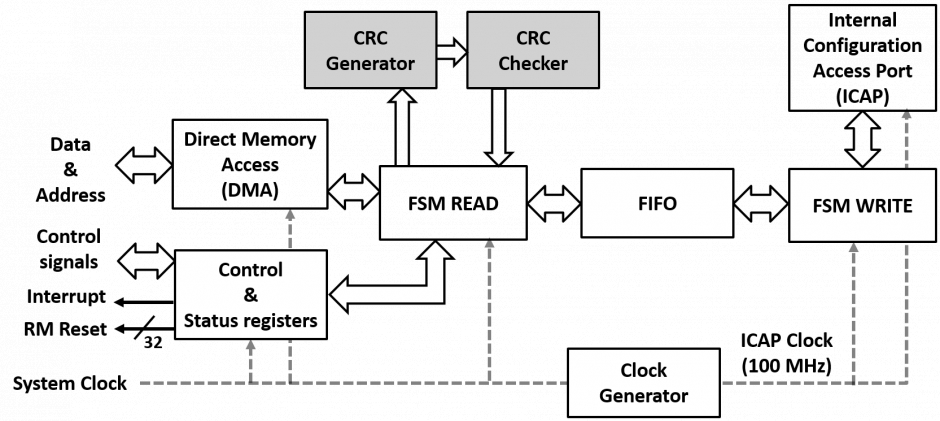

The Dynamic Partial Reconfiguration Controller (DPRC) enables self run-time partial reconfiguration of Xilinx Virtex-4/5/6 and 7Series FPGAs through the AMBA AHB and the Internal Configuration Access Port (ICAP).s.

DPRC has been developed in collaboration with Cobham Gaisler AB (www.gaisler.com). It is part of Cobham Gaisler GRLIB open-source IP cores library.

The GRLIB IP Library is an integrated set of reusable IP cores, designed for system-on-chip (SoC) development. Some examples are: the LEON3 processor, communication interfaces (e.g., Ethernet and PCI controllers) and memory controllers (e.g., SDRAM, DDR, DDR2).

The library includes DPRC full source code (VHDL), associated documentation, and examples of how to create LEON3-based dynamically reconfigurable systems on Xilinx FPGAs.

The main characteristics of DPRC are:

- support for the most popular Xilinx FPGA device families (i.e., Virtex-4/5/6 and 7 Series);

- configurable through VHDL generics in different operating modes, depending on user requirements;

- optional and configurable CRC-based error detection mechanism on partial bitstreams;

- DMA interface to allow fast reconfiguration;

- software-centric interface with control/status registers that can be mapped on the processor bus.

Developers

Pascal Trotta

How to cite DPRC

The TestGroup development team has invested a lot of time and effort in creating DPRC as it is today. Please give credit where credit is due and cite DPRC when you use it for your research activities.

DPRC can be cited through this papers:

S. Di Carlo, P. Prinetto, P. Trotta and J. Andersson, “A portable open-source controller for safe Dynamic Partial Reconfiguration on Xilinx FPGAs,” 2015 25th International Conference on Field Programmable Logic and Applications (FPL), London, 2015, pp. 1-4. doi: 10.1109/FPL.2015.7294002

BibTEX

@INPROCEEDINGS{7294002,

author={S. Di Carlo and P. Prinetto and P. Trotta and J. Andersson},

booktitle={2015 25th International Conference on Field Programmable Logic and Applications (FPL)},

title={A portable open-source controller for safe Dynamic Partial Reconfiguration on Xilinx FPGAs},

year={2015},

pages={1-4},

keywords={SRAM chips;error correction;error detection;field programmable gate arrays;integrated circuit design;logic design;DPR;HDL source code;SRAM-based field programmable gate array devices;Xilinx FPGAs;configurable error correction circuitry;configurable error detection circuitry;hardware design phase;low nonrecurrent engineering costs;open-source Cobham Gaisler GRLIB IP-cores library;partial bitstream data errors;portable open-source controller;safe dynamic partial reconfiguration process;Clocks;Field programmable gate arrays;Hardware;Monitoring;Process control;Reliability;Throughput},

doi={10.1109/FPL.2015.7294002},

ISSN={1946-147X},

month={Sept},}

Downloads

DPRC is part of Cobham Gaisler GRLIB open-source IP cores library that can be downloaded at the following link: http://www.gaisler.com/index.php/downloads/leongrlib (GPL version)