Concluded in Autumn 2016, the EU-funded CLERECO (Cross Layer Early Reliability Evaluation for the Computing cOntinuum) project proposed a lucalable, cross-layer methodology and supporting suite of tools for accurate and fast estimations of computing systems’ reliability.

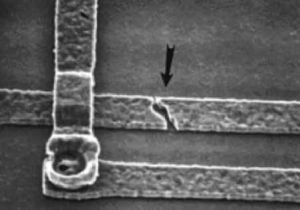

As we enter the era of nanoscale devices, reliability is becoming a key challenge for the semiconductor industry. The now atomic dimensions of transistors result in a vulnerability to variations in the manufacturing process and can dramatically increase the effect of environmental stress on the correct circuit behaviour. Failures in early assessing computing systems’ reliability may produce excessive redesign costs which can have severe consequences for the success of a product.

As we enter the era of nanoscale devices, reliability is becoming a key challenge for the semiconductor industry. The now atomic dimensions of transistors result in a vulnerability to variations in the manufacturing process and can dramatically increase the effect of environmental stress on the correct circuit behaviour. Failures in early assessing computing systems’ reliability may produce excessive redesign costs which can have severe consequences for the success of a product.

Current practice involves a worst-case design approach with large guard bands. Unfortunately, application of this approach is reaching its limit in terms of economic sustainability with regard to performance, size and energy costs.

Current practice involves a worst-case design approach with large guard bands. Unfortunately, application of this approach is reaching its limit in terms of economic sustainability with regard to performance, size and energy costs.

Coordinated by Dr Stefano Di Carlo of the Polytechnic of Turin, the CLERECO project aimed to address this challenge by focusing on reliability analysis in the early phases of the design. Early assessment within the design cycle provides the freedom for adaptive modification if the estimated reliability level does not meet the requirements. CLERECO methodology provides dedicated tools to separately analyse the technology, the hardware components (at the microarchitecture level) and the software modules of a complex system and to recombine the characteristics of single objects into a complex statistical Bayesian model. This can be used to perform statistical reasoning on the reliability of the system as a whole.

See the full version of this story at:

The CLERECO project was a successful experience with top-tier ACM/IEEE publications and an eco-system of integrated tools delivered. Thanks to all partners PoliTo, UoA, UPC, CNRS, Thales, ABB, Intel/Yogitech for great contributions.

Stefano Di CARLO